FPGA软件测试工具软件

1,名词解释

FPGA(Field-Programmable Gate Array),即现场可编程门阵列

以硬件描述语言(Verilog或VHDL)所完成的电路设计,可以经过简单的综合与布局布线,快速的下载到 FPGA 上进行软件测试,是现代 IC设计验证的技术主流。这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块。

专用集成电路

英文全称:Application Specific Integrated Circuit 简称ASIC

专用集成电路是为特定用户或特定电子系统制作的集成电路。数字集成电路的通用性和大批量生产,使电子产品成本大幅度下降,推进了计算机通信和电子产品的普及,但同时也产生了通用与专用的矛盾,以及系统设计与电路制作脱节的问题。同时,集成电路规模越大,组建系统时就越难以针对特殊要求加以改变。为解决这些问题,就出现了以用户参加设计为特征的专用集成电路,它能实现整机系统的优化设计,性能优越,保密性强。

RTL code: Register-Transfer-Level code

通常由VHDL/verilog两种语言进行描述

RTL仿真器

就是使用Verilog语言进行RTL级代码的编写。RTL是寄存器传输级的意思,包括了可综合的数据流级和行为级,是最常用的编程风格。

这一行业都是使用Verilog语言编程,对输入信号进行采集、处理等工作,然后控制各种外围部件,和单片机差不多,只不过资源丰富一点、速度快一点、功能强大一点而已;或者是设计ASIC,并进行验证

HDL是一种硬件描述语言(HDL:Hardware Discription Language)

HDL是一种硬件描述语言(HDL:Hardware Discription Language),是一种以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

VHDL全名Very-High-Speed Integrated Circuit Hardware Description Language

诞生于1982年。1987年底,VHDL被IEEE和美国国防部确认为标准硬件描述语言 。 VHDL和Verilog作为IEEE的工业标准硬件描述语言,得到众多EDA公司支持,在电子工程领域,已成为事实上的通用硬件描述语言。

Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language)

以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

Synopsys

是为全球集成电路设计提供电子设计自动化(EDA)软件工具的主导企业。为全球电子市场提供技术先进的IC设计与验证平台,致力于复杂的芯片上系统(SoCs)的开发。

2,FPGA测试工具软件介绍

随着FPGA(Field Programmable Gate Array)器件的应用越来越广泛且重要,

FPGA的软件测试技术也得到了广泛重视和研究。基于FPGA可编程的特性,应用独立的软件测试(工厂软件测试)需要设计数个软件测试编程和软件测试向量来完成FPGA的软件测试,

确保芯片在任何用户可能的编程下都可靠工作。

自1984年Xilinx公司发明FPGA至今,FPGA已经历了十几年的发展历史。

在这十几年的发展过程中,以FPGA为代表的数字系统现场集成技术取得了惊人的发展:现场可编程逻辑器件从最初的1200个可利用门,发展到90年代的25万个可利用门,乃至现在,国际上现场可编程逻辑器件的著名厂商又陆续推出了数百万门的单片FPGA芯片,将现场可编程器件的集成度提高到一个新的水平。

目前FPGA软件测试工具分为:

l Certify基于多个FPGA的分割、物理综合及调试工具;

l Leda RTL Checker编码规则检查器;

l VCS RTL Verification数字逻辑仿真验证工具;

l Formality等效性检测工具;

l PrimeTime,门级静态时序分析;

l Identify Pro 全设计可视化的调试工具。

Certify基于多个FPGA的分割、物理综合及调试工具

Certify可以确保得到最佳的RTL验证的性能。这是唯一的一个能够同时做多个FPGA之间的时延分析和物理综合的FPGA原型验证的工具——优化了整个原型验证的性能,而不是单独的FPGA.使用Certify,用户只需花费几天的时间就可以把用来验证的RTL代码转到多片可以完成相同功能的FPGA上去。与此相比,传统的方法则要花数月的时间。使用Certify,可以在不到一个月的时间内建立完成一个完全基于FPGA的硬件原型验证,这只是硬件仿真器价格的一小部分,同时还可以得到极佳的验证性能。Certify已经可以支持所有的硬件原型验证系统,如可重构原型验证硬件盒,标准的原型验证预定义板。

Certify中的物理综合工具Synplify Premier使用最小的逻辑资源满足设计人员需求,FPGA供应商如Xilinx,Altera,Actel也建议自己的工程师及客户选择该工具进行项目的综合。Premier 区别于传统的逻辑综合技术,在综合的同时完成了整体的布局,并进行预布线操作,输出的网表带有布局信息,到后续vendor的工具可完成布线,大大提升了逻辑的性能,用最小的逻辑资源跑最快的速度。

Synplify Premier的流程与传统的逻辑综合流程完全一致,只是在MAPPING的过程中完成了整体布局及预布线动作,几乎所有的工作量都有软件在后台完成,不会增加工程师额外的工作量。同时又增加了可视化的物理级别的分析界面,可以非常清晰的了解自己的设计在芯片当中的布局,有助于提升整体的运行时间。

LEDA是一种可编程代码设计规则检查器

它提供全芯片级混合语言(Verilog和VHDL)处理能力,从而加快了复杂设计的开发。LEDA预装的检查规则大大地增强了设计人员检查HDL代码的能力,包括可综合性,可仿真性、可软件测试性和可重用性。使用LEDA,可以对硬件设计的仿真和综合进行预检查,消除设计流程中的瓶颈,其中Verilog代码设计规则可确保按内部或外部工具要求优化代码

。LEDA提供的设计规则可提高Synopsys工具的性能。

主要特点:

l 支持Verilog/VHDL混合语言的设计;

l 包含先进的硬件设计推测和层次化检查的能力,确保设计人员对特殊硬件结构(包括时钟、寄存器、锁存器)进行规则检查;

l 包括预装全面的设计规则检查和规范集;

l 针对Synopsys工具性能优化的HDL代码检查,以确保与工具(如Design Compiler、VCS, Formality, Synplify )的最新功能要求兼容。

VCS RTL Verification数字逻辑仿真验证工具

VCS 数字逻辑仿真器和VCS MX混合HDL语言仿真器都是Synopsys的智能RTL验证解决方案的基石。VCS是业界领先的仿真器,支持本征断言(native assertion)描述、自动软件测试平台生成技术(testbench)、以及代码和断言覆盖引擎,确保智能化验证的实现。VCS中本征代码支持(Native)技术确保了设计验证的效率、性能和质量,并缩短了验证周期。VCS中的本征代码技术实现了在单一工具中,支持可验证性设计(DFV),及覆盖率驱动和约束的随机激励生成。其本征对断言的支持和所包含的丰富的断言检查工具库保证了设计人员能够方便地采用DFV技术来查找错误和提高验证质量。此外,断言可以作为设计要求重复利用,在Synopsys的混合RTL规则验证产品Magellan中进行形式验证。

VCS对专用集成电路(ASIC)生产商的建模和仿真签核(Sign-off)提供了支持。 VCS对统一的设计和验证语言标准SystemVerilog提供支持。

对于要求在RTL环境中使用SystemC模型进行验证的设计团队,VCS提供了支持OSCI SystemC的直接内核接口(DKI)和支持System Studio的直接内核接口(DKI)。

主要优势:

l 本征软件测试平台(testbench)、断言和完备的覆盖率软件测试技术,为Verilog 和混合HDL验证带来2-5倍的性能提升;

l 为SystemVerilog设计和基于断言的验证提供支持,确保更高的设计和验证效率;

l 提供最高的性能和容量,加快产品上市周期;

l 采用单个统一工具,实现Verilog和混合HDL RTL及SystemC的支持,支持所有主要的UNIX和Linux平台 。

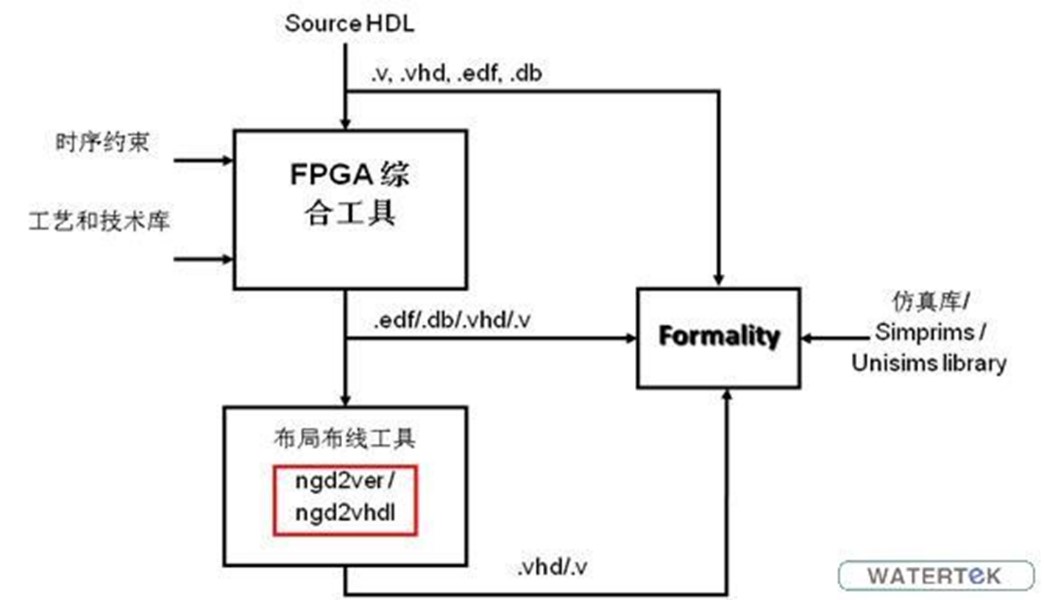

Formality等效性检测工具

Formality采用形式验证的技术来判断一个设计的两个版本在功能上是否等效。等效性检测是一种静态分析方法,无需软件测试向量即可快速而全面的完成验证。

Formality具有一个流程化的图形界面和先进的调试功能,令设计者可以很快地检测出设计中地错误并将之隔离,这一功能可以大大缩短得到验证结果所需的时间。Formality业界领先的功能和性能使之成为设计团队的首选产品。

产品优势:

l 通过完备的验证覆盖将流片失败的可能性降到最低 ;

l 对一个几百万门的设计进行验证以分钟记数,加快了产品上市时间;

l 降低了工具设置的需求并提供快速错误隔离的功能,显著的缩短了传统的等效性检测的周期 ;

l 提供了为业界所证实的先进功能,能充分利用现有的硬件资源。

图1 Formality等效性检测工具

PrimeTime 全芯片,门级静态时序分析

PrimeTime 是针对复杂的10千万门全芯片门级静态时序分析器。PrimeTime能进行静态时序分析(STA),精确的RC延迟计算,先进的建模和时序验收。对于大型的多时钟的设计,比如包括了综合出的逻辑电路、嵌入式存储器和微处理器核的设计,这是一个理想的工具。

产品优势:

l 64bit的体系结构允许完成超过10千万门级设计的时序分析增量分析减少了小的设计修改所需的运行时间,提高了效率;

l 精确的RC延迟计算使用SPEF,DSPF和RSPF中的寄生参数,还可以使用二进制的寄生参数文件以便于有效传输;

l 先进的建模能力支持层次化的STA 验收和基于单元的可复用IP的建模是所有主要的ASIC、FPGA供应商所支持的时序验收工具。

Identify Pro 全设计可视化的调试工具

Synopsys的Identify工具允许FPGA设计者以一种类似于RTL仿真器的方式对硬件进行调试。在这种方式下,设计者可以在RTL源码中直接地控制硬件的触发点,并且可以在源码中直接地看到并且采集到的数据。这种便利常常可以将本来所需的几周到几个月的时间,缩短到只有几天。

【投稿】【关闭窗口】【打印】